Министерство образования и науки Украины

Государственное высшее учебное заведение

«Национальный горный университет»

Институт электроэнергетики

Кафедра электропривода

**Лабораторные работы**

**по дисциплине**

**«Схемотехническое проектирование**

**в Электромеханике»**

Днепропетровск

2013

## Лабораторная работа №1

**Тема:** Графическое введение принципиальной схемы комбинационного логического устройства, которое описано булевым уравнением.

Реализовать на базе ПЛИС фирмы Altera серии MAX 7000 логическое устройство комбинационного типа, смоделировать его работу. Вариант задания совпадает с номером студента в журнале группы. Ввод проекта осуществлять в графическом редакторе в соответствии с заданным логическим уравнением. Предварительную минимизацию логических уравнений не производить.

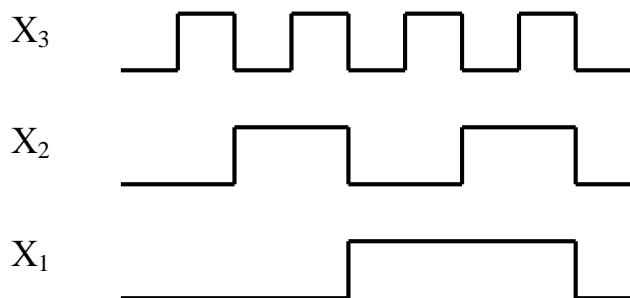

При моделировании тестовые сигналы подавать на входы устройства в таком порядке:

| Вариант | Формулы логических уравнений                                                                                                 |

|---------|------------------------------------------------------------------------------------------------------------------------------|

| 1       | $Y = X_1 \cdot X_2 + (\overline{X_1 \cdot X_2 \cdot \overline{X_3}}) \cdot (X_2 + \overline{X_3})$                           |

| 2       | $Y = (X_2 \cdot \overline{X_3} + X_1) \cdot (\overline{\overline{X}_2 + X_3}) + (\overline{X_1 \cdot X_3})$                  |

| 3       | $Y = X_1 \cdot \overline{X}_2 \cdot X_3 + X_1 \cdot (\overline{X_2 \cdot \overline{X}_3}) + X_2 \cdot X_3$                   |

| 4       | $Y = (\overline{X_1 \cdot \overline{X}_3}) + X_2 \cdot \overline{X}_3 + (\overline{X_1 \cdot X_2}) \cdot X_3$                |

| 5       | $Y = (\overline{X}_1 + (\overline{X_2 + X_3})) \cdot (X_1 + X_3) \cdot (\overline{X_1 + X_2 + \overline{X}_3})$              |

| 6       | $Y = (\overline{X_2 \cdot \overline{X}_3}) \cdot (X_1 + X_3 \cdot \overline{X}_2) \cdot (\overline{X}_1 + X_2)$              |

| 7       | $Y = X_1 \cdot (X_2 + (\overline{\overline{X}_3 \cdot X_1})) + (\overline{X_2 \cdot \overline{X}_3}) \cdot X_3$              |

| 8       | $Y = X_2 \cdot \overline{X}_3 \cdot X_1 + (\overline{\overline{X}_1 \cdot X_2 \cdot X_3}) + X_1 \cdot X_2$                   |

| 9       | $Y = (\overline{X}_1 \cdot X_2 \cdot X_3 + (\overline{X_1 \cdot X_2})) \cdot X_2 + X_3 \cdot \overline{X}_1$                 |

| 10      | $Y = (((\overline{X_2 \cdot \overline{X}_3}) + X_1) \cdot (\overline{X_1 \cdot \overline{X}_2}) + X_3) \cdot \overline{X}_2$ |

$$\begin{aligned}11 \quad Y &= (X_1 \cdot X_3 + \bar{X}_2 \cdot \bar{X}_3) \cdot (\overline{\bar{X}_1 + X_3}) \cdot X_1 \\12 \quad Y &= ((\overline{X_1 \cdot X_2}) \cdot X_3 + X_1) \cdot (\overline{\bar{X}_2 + X_3 \cdot \bar{X}_2}) \cdot X_1 \\13 \quad Y &= \left( \left( \overline{\overline{X_1 \cdot X_2}} \cdot X_3 \right) + X_2 \cdot \bar{X}_3 \right) \cdot (X_1 + X_3) \\14 \quad Y &= (\bar{X}_1 \cdot (\overline{\bar{X}_2 \cdot X_3}) + X_2) \cdot (\overline{X_1 \cdot \bar{X}_3}) \\15 \quad Y &= (\overline{\bar{X}_1 + X_2 + \bar{X}_3}) \cdot X_2 + (\overline{\bar{X}_3 \cdot X_1}) \\16 \quad Y &= \bar{X}_1 \cdot X_2 \cdot \bar{X}_3 \cdot ((\overline{X_2 \cdot X_3}) + X_1 \cdot \bar{X}_2) \\17 \quad Y &= ((\overline{X_1 + X_2}) \cdot X_3 + (\overline{\bar{X}_1 \cdot X_2})) \cdot (\overline{X_2 + X_3}) \\18 \quad Y &= (X_1 \cdot \bar{X}_2 + X_2 \cdot \bar{X}_3 + \bar{X}_1 \cdot X_3) \cdot (X_1 + X_3)\end{aligned}$$

## Лабораторная работа №2

**Тема:** Графическое введение и анализ принципиальной схемы комбинационного логического устройства с использованием различных способов сопряжения элементов.

Реализовать на базе ПЛИС фирмы Altera серии MAX 9000 в корпусе с 208-ю ножками заданное логическое устройство комбинационного типа, смоделировать его работу, произвести временной анализ. Все внешние сигналы разместить на ножках микросхемы со 160-й по 190-ю.

Описание устройства осуществлять в графическом редакторе. При вводе проекта ориентироваться на использование в качестве соединителей одинаковых имен выводов элементов. По возможности задавать входы и выходы устройства как шины. При создании файла тестовых воздействий для моделирования устройства сигналы, входящие в состав шин, вводить как шины.

Вариант задания совпадает с номером студента в журнале группы.

| <b>Вариант</b> | <b>Комбинационное логическое устройство</b>                                                                  |

|----------------|--------------------------------------------------------------------------------------------------------------|

| 1.             | Шифратор на 10 входов и выходной шиной из 4-х сигналов в двоичной системе                                    |

| 2.             | Шифратор на 16 входов и выходной шиной из 4-х сигналов в двоичной системе                                    |

| 3.             | Шифратор на 16 входов и выходной шиной из 5-ти сигналов в двоично-десятичной системе                         |

| 4.             | Шифратор на 20 входов и выходной шиной из 5-ти сигналов в двоичной системе                                   |

| 5.             | Шифратор на 20 входов и выходной шиной из 5-ти сигналов в двоично-десятичной системе                         |

| 6.             | Дешифратор с входной шиной из 3-х сигналов в двоичной системе, на 8 выходов                                  |

| 7.             | Дешифратор с входной шиной из 4-х сигналов в двоичной системе, на 10 выходов                                 |

| 8.             | Дешифратор с входной шиной из 4-х сигналов в двоичной системе, на 16 выходов                                 |

| 9.             | Дешифратор с входной шиной из 5-ти сигналов в двоично-десятичной системе, на 16 выходов                      |

| 10.            | Мультиплексор с шиной данных на 8 входов, шиной адреса на 3 входа в двоичной системе и одним выходом данных  |

| 11.            | Мультиплексор с шиной данных на 10 входов, шиной адреса на 4 входа в двоичной системе и одним выходом данных |

12. Мультиплексор с шиной данных на 16 входов, шиной адреса на 4 входа в двоичной системе и одним выходом данных

13. Мультиплексор с шиной данных на 16 входов, шиной адреса на 5 входов в двоично-десятичной системе и одним выходом данных

14. Демультиплексор с одним входом данных, шиной адреса на 3 входа в двоичной системе и шиной данных на 8 выходов

15. Демультиплексор с одним входом данных, шиной адреса на 4 входа в двоичной системе и шиной данных на 10 выходов

16. Демультиплексор с одним входом данных, шиной адреса на 4 входа в двоичной системе и шиной данных на 16 выходов

17. Демультиплексор с одним входом данных, шиной адреса на 5 входов в двоично-десятичной системе и шиной данных на 16 выходов

18. Преобразователь кодов из двоичной в двоично-десятичную систему с входной шиной из 4-х сигналов и выходной из 5-ти сигналов

19. Преобразователь кодов из двоично-десятичной в двоичную систему с входной шиной из 5-ти сигналов и выходной из 4-х сигналов

20. Преобразователь кодов из двоичной в двоично-десятичную систему с входной шиной из 5-ти сигналов и выходной из 5-ти сигналов

21. Преобразователь кодов из двоично-десятичной в двоичную систему с входной шиной из 5-ти сигналов и выходной из 5-ти сигналов

Пример формул логических уравнений шифратора с 10-ю входными сигналами и выходной шиной из 4-х сигналов:

$$Q_0 = X_1 + X_3 + X_5 + X_7 + X_9;$$

$$Q_1 = X_2 + X_3 + X_6 + X_7;$$

$$Q_2 = X_4 + X_5 + X_6 + X_7;$$

$$Q_3 = X_8 + X_9$$

Пример формул логических уравнений дешифратора с входной шиной из 4-х сигналов и 10-ю выходными сигналами

$$Y_0 = \overline{Q}_0 \cdot \overline{Q}_1 \cdot \overline{Q}_2 \cdot \overline{Q}_3;$$

$$Y_1 = Q_0 \cdot \overline{Q}_1 \cdot \overline{Q}_2 \cdot \overline{Q}_3;$$

$$Y_2 = \overline{Q}_0 \cdot Q_1 \cdot \overline{Q}_2 \cdot \overline{Q}_3;$$

$$Y_3 = Q_0 \cdot Q_1 \cdot \overline{Q}_2 \cdot \overline{Q}_3;$$

$$Y_4 = \overline{Q}_0 \cdot \overline{Q}_1 \cdot Q_2 \cdot \overline{Q}_3;$$

$$Y_5 = Q_0 \cdot \overline{Q}_1 \cdot Q_2 \cdot \overline{Q}_3;$$

$$Y_6 = \overline{Q}_0 \cdot Q_1 \cdot Q_2 \cdot \overline{Q}_3;$$

$$Y_7 = Q_0 \cdot Q_1 \cdot Q_2 \cdot \overline{Q}_3;$$

$$Y_8 = \overline{Q}_0 \cdot \overline{Q}_1 \cdot \overline{Q}_2 \cdot Q_3;$$

$$Y_9 = Q_0 \cdot \overline{Q}_1 \cdot \overline{Q}_2 \cdot Q_3$$

## Лабораторная работа №3

**Тема:** Создание и анализ проекта комбинационного логического устройства с помощью описания задания в редакторе временных диаграмм.

Реализовать на базе ПЛИС фирмы Altera серии FLEX 8000 в корпусе со 160-я ножками заданное логическое устройство комбинационного типа, смоделировать его работу, произвести временной анализ. Все внешние сигналы разместить на ножках микросхемы со 120-й по 160-ю.

Описание устройства осуществлять в редакторе временных диаграмм. По возможности задавать входы и выходы устройства как шины. При создании файла тестовых воздействий для моделирования устройства сигналы, входящие в состав шин, вводить как шины.

Вариант задания совпадает с номером студента в журнале группы.

| <b>Вариант</b> | <b>Комбинационное логическое устройство</b>                                                                                 |

|----------------|-----------------------------------------------------------------------------------------------------------------------------|

| 1.             | Демультиплексор с одним входом данных, шиной адреса на 3 входа в двоичной системе и шиной данных на 8 выходов               |

| 2.             | Демультиплексор с одним входом данных, шиной адреса на 4 входа в двоичной системе и шиной данных на 10 выходов              |

| 3.             | Демультиплексор с одним входом данных, шиной адреса на 4 входа в двоичной системе и шиной данных на 16 выходов              |

| 4.             | Демультиплексор с одним входом данных, шиной адреса на 5 входов в двоично-десятичной системе и шиной данных на 16 выходов   |

| 5.             | Преобразователь кодов из двоичной в двоично-десятичную систему с входной шиной из 4-х сигналов и выходной из 5-ти сигналов  |

| 6.             | Преобразователь кодов из двоично-десятичной в двоичную систему с входной шиной из 5-ти сигналов и выходной из 4-х сигналов  |

| 7.             | Преобразователь кодов из двоичной в двоично-десятичную систему с входной шиной из 5-ти сигналов и выходной из 5-ти сигналов |

| 8.             | Преобразователь кодов из двоично-десятичной в двоичную систему с входной шиной из 5-ти сигналов и выходной из 5-ти сигналов |

| 9.             | Шифратор на 10 входов и выходной шиной из 4-х сигналов в двоичной системе                                                   |

10. Шифратор на 16 входов и выходной шиной из 4-х сигналов в двоичной системе

11. Шифратор на 16 входов и выходной шиной из 5-ти сигналов в двоично-десятичной системе

12. Шифратор на 20 входов и выходной шиной из 5-ти сигналов в двоичной системе

13. Шифратор на 20 входов и выходной шиной из 5-ти сигналов в двоично-десятичной системе

14. Дешифратор с входной шиной из 3-х сигналов в двоичной системе, на 8 выходов

15. Дешифратор с входной шиной из 4-х сигналов в двоичной системе, на 10 выходов

16. Дешифратор с входной шиной из 4-х сигналов в двоичной системе, на 16 выходов

17. Дешифратор с входной шиной из 5-ти сигналов в двоично-десятичной системе, на 16 выходов

18. Мультиплексор с шиной данных на 8 входов, шиной адреса на 3 входа в двоичной системе и одним выходом данных

19. Мультиплексор с шиной данных на 10 входов, шиной адреса на 4 входа в двоичной системе и одним выходом данных

20. Мультиплексор с шиной данных на 16 входов, шиной адреса на 4 входа в двоичной системе и одним выходом данных

21. Мультиплексор с шиной данных на 16 входов, шиной адреса на 5 входов в двоично-десятичной системе и одним выходом данных

## Лабораторная работа №4

**Тема:** Создание и анализ проекта последовательного логического устройства посредством использования библиотеки параметризованных модулей.

Реализовать на базе ПЛИС фирмы Altera серии MAX 7000A в корпусе с 144-я ножками заданное логическое устройство последовательного типа, смоделировать его работу, произвести временной анализ. Все внешние сигналы разместить на ножках микросхемы с 100-й по 140-ю.

Описание устройства осуществлять в графическом редакторе с использованием библиотеки параметрических модулей. По возможности задавать входы и выходы устройства как шины. При создании файла тестовых воздействий для моделирования устройства сигналы, входящие в состав шин, вводить как шины.

Вариант задания совпадает с номером студента в журнале группы.

| <b>Вариант</b> | <b>Последовательное логическое устройство</b>                                                |

|----------------|----------------------------------------------------------------------------------------------|

| 1.             | Параллельный регистр на 8 ячеек                                                              |

| 2.             | Параллельный регистр на 16 ячеек                                                             |

| 3.             | Сдвигающий регистр на 8 ячеек                                                                |

| 4.             | Сдвигающий регистр на 16 ячеек                                                               |

| 5.             | Универсальный регистр на 8 ячеек                                                             |

| 6.             | Универсальный регистр на 16 ячеек                                                            |

| 7.             | Двоичный суммирующий счетчик с последовательным переносом и выходной шиной из 4-х сигналов   |

| 8.             | Двоичный суммирующий счетчик с параллельным переносом и выходной шиной из 4-х сигналов       |

| 9.             | Двоичный вычитающий счетчик с последовательным переносом и выходной шиной из 4-х сигналов    |

| 10.            | Двоичный вычитающий счетчик с параллельным переносом и выходной шиной из 4-х сигналов        |

| 11.            | Двоичный универсальный счетчик с последовательным переносом и выходной шиной из 4-х сигналов |

| 12.            | Двоичный универсальный счетчик с параллельным переносом и выходной шиной из 4-х сигналов     |

| 13.            | Распределитель тактов с 8-ю выходами                                                         |

| 14.            | Распределитель тактов с 10-ю выходами                                                        |

| 15.            | Распределитель тактов с 12-ю выходами                                                        |

| 16.            | Распределитель тактов с 16-ю выходами                                                        |

17. Распределитель тактов с 20-ю выходами

18. Распределитель тактов с 24-я выходами

## **Лабораторная работа №5**

**Тема:** Создание и анализ проекта запоминающего устройства RAM.

Реализовать на базе ПЛИС фирмы Altera серии FLEX 6000 в корпусе с 240-а ножками заданное устройство памяти RAM, смоделировать его работу, произвести временной анализ. Все внешние сигналы разместить на ножках микросхемы с 50-й по 200-ю.

Описание устройства осуществлять в графическом редакторе и в редакторе временных диаграмм. По возможности задавать входы и выходы устройства как шины.

Реализацию устройства памяти RAM начать с создания проектов нижнего уровня иерархии: REGISTR, DESHIFR\_CS (создать в графическом редакторе), DESHIFR\_2\_4 (создать в редакторе временных диаграмм). Затем с использованием этих подпроектов в графическом редакторе создается проект верхнего уровня иерархии устройства памяти RAM.

При создании файла тестовых воздействий для моделирования устройства сигналы, входящие в состав шин, вводить как шины.

Тестирование работы устройства осуществить записывая и считывая различную информацию по определенным адресам ячеек памяти, причем следует проверить работу RAM как с существующими заданными ячейками памяти, так и с реально не реализованными.

Вариант задания совпадает с номером студента в журнале группы.

| <b>Вариант</b> | <b>Запоминающее устройство RAM</b>   |

|----------------|--------------------------------------|

| 1.             | На 4-е ячейки с адресами 0008h-000Bh |

| 2.             | На 4-е ячейки с адресами 0070h-0073h |

| 3.             | На 4-е ячейки с адресами 0254h-0257h |

| 4.             | На 4-е ячейки с адресами 06A0h-06A3h |

| 5.             | На 4-е ячейки с адресами 0AE8h-0AEBh |

| 6.             | На 4-е ячейки с адресами 0FC4h-0FC7h |

| 7.             | На 4-е ячейки с адресами 024Ch-024Fh |

| 8.             | На 4-е ячейки с адресами 04C0h-04C3h |

| 9.             | На 4-е ячейки с адресами 000Ch-000Fh |

| 10.            | На 4-е ячейки с адресами 0138h-013Bh |

| 11.            | На 4-е ячейки с адресами 0200h-0203h |

| 12.            | На 4-е ячейки с адресами 02C8h-02CBh |

| 13.            | На 4-е ячейки с адресами 03A0h-03A3h |

14. На 4-е ячейки с адресами 05D8h-05DBh

15. На 4-е ячейки с адресами 0AF0h-0AF3h

16. На 4-е ячейки с адресами 0BCCh-0BCFh

17. На 4-е ячейки с адресами 0C64h-0C67h

18. На 4-е ячейки с адресами 0EACH-0EAfh

## Лабораторная работа №6

**Тема:** Создание и анализ проекта арифметико-логического устройства с использованием библиотеки мегафункций.

Реализовать на базе ПЛИС фирмы Altera серии FLEX 10K в корпусе с 240-а ножками заданное арифметико-логическое устройство, смоделировать его работу, произвести временной анализ. Все внешние сигналы разместить на ножках микросхемы со 180-й по 240-ю.

Описание устройства осуществлять в графическом редакторе с использованием библиотеки мегафункций. По возможности задавать входы и выходы устройства как шины. При создании файла тестовых воздействий для моделирования устройства сигналы, входящие в состав шин, вводить как шины.

Вариант задания совпадает с номером студента в журнале группы.

| <b>Вариант</b> | <b>Арифметико-логическое устройство</b>                                                                           |

|----------------|-------------------------------------------------------------------------------------------------------------------|

| 1.             | Четырехразрядный последовательный синхронный сумматор с параллельным переносом                                    |

| 2.             | Четырехразрядный последовательный асинхронный сумматор с параллельным переносом                                   |

| 3.             | Четырехразрядный последовательный синхронный сумматор с последовательным переносом                                |

| 4.             | Четырехразрядный последовательный асинхронный сумматор с последовательным переносом                               |

| 5.             | Четырехразрядный параллельный синхронный сумматор с параллельным переносом                                        |

| 6.             | Четырехразрядный параллельный асинхронный сумматор с параллельным переносом                                       |

| 7.             | Четырехразрядный параллельный синхронный сумматор с последовательным переносом                                    |

| 8.             | Четырехразрядный параллельный асинхронный сумматор с последовательным переносом                                   |

| 9.             | Четырехразрядный параллельный синхронный сумматор с групповой структурой и цепным переносом                       |

| 10.            | Четырехразрядный параллельный асинхронный сумматор с групповой структурой и цепным переносом                      |

| 11.            | Четырехразрядный последовательный синхронный сумматор с групповой структурой и параллельно-параллельным переносом |

12. Четырехразрядный последовательный асинхронный сумматор с групповой структурой и параллельно-параллельным переносом

13. Четырехразрядный параллельный синхронный умножитель

14. Четырехразрядный параллельный асинхронный умножитель

15. Четырехразрядный параллельный синхронный двоично-десятичный сумматор

16. Четырехразрядный параллельный асинхронный двоично-десятичный сумматор

17. Четырехразрядный последовательный синхронный двоично-десятичный сумматор

18. Четырехразрядный последовательный асинхронный двоично-десятичный сумматор